risc-v-RISC-V指令格式

推荐 原创本文属于《 RISC-V指令集基础系列教程》之一,欢迎查看其它文章。

1 RISC-V指令集命名规范

前面提到过RV32I,这是什么含义呢?

我们看看RISC-V的命名规范,是如何定义的,就明白了。

RISC-V命名规范:RV[###][abc……xyz]

- RV:用于标识 RISC-V 体系架构的前缀,即 RISC-V 的缩写。

- [###]:用于标识处理器的字宽,也就是 处理器的寄存器宽度(单位为 bit),通常可以为32、64、128。

- [abc…xyz]:标识该处理器支持的,指令集模块集合。

因此,RV32I,表示RISC-V的32位整数指令集,它是RISC-V 的核心,是冻结的,永远不会改变。

也就是说,RISC-V的所有指令集合名称,全部是以RV打头,加位宽,加模块名来组成的,后续识别也就很简单了。

2 RISC-V指令集组成

RISC-V指令集,是以一个基础整数指令集,为核心模块,根据需要再选择多个扩展指令集,组合而成的。

用一个公式简单表达,即:

RISC-V指令集 = 1个基础整数指令集 + 多个可选的扩展指令集

在RISC-V指令集架构中,G表示通用组合,全称为RV32G(32位)或RV64G(64位)。这个通用组合由一系列指令子集模块组成,其中包括I、M、A、D、F等模块。这些模块组合在一起,形成一个完整的指令集。

因此,G是RISC-V指令集架构中通用处理器所包含的指令集的表示。

也就是说,用公式表示,即:

G = I + M + A + D + F

I表示基础整数指令集;M/A/D/F表示具体扩展指令集,含义见后续。

2.1 基础整数指令集

基础指令集是固定的,永远不会改变。扩展指令集类似一种插件的思想。

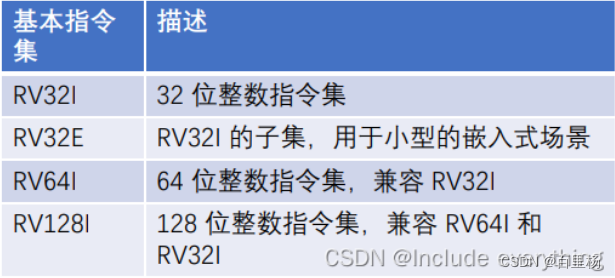

RISC-V协议规定的,基础整数指令集,一共有4种,如下所示:

高字长的基础整数指令集向下兼容。

其中嵌入式指令集(Embedded)是基础整数指令集的子集,在一些小型的嵌入式场景中适用。

设计时,只需要从4种指令集中,任选一种即可。

目前RV128I,需要根据实际使用来改进设计规范,因此尚未冻结。

2.2 扩展指令集

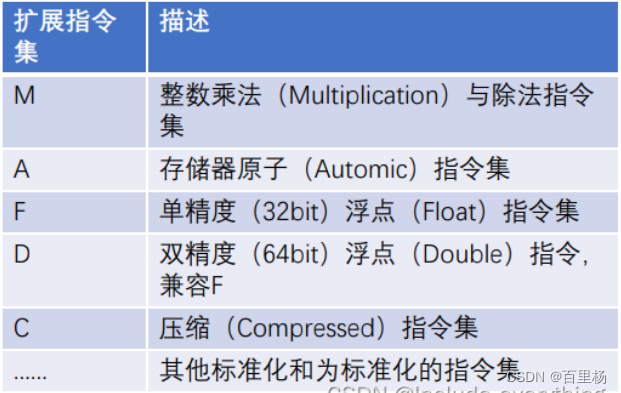

RISC-V 允许在实现中以可选的形式实现,其他标准化和非标准化的指令集扩展。

RISC-V协议规定的,扩展指令集,就比较多了,如下所示:

- M:乘法和除法指令(RV32M,RV64M)

- A:原子指令(RV32A,RV64A)

- F:单精度浮点指令(RV32F,RV64F)

- D:双精度浮点指令(RV32D,RV64D)

特定组合“IMAFD”被称为 “通用(General)”组合,用英文字母 G 表示,比如:

它们与RV32I统称为RV32G,或者与RV64I统称为RV64G。

RV32G,表示32位RISC-V通用处理器,指令集组合。

RV64G,表示64位RISC-V通用处理器,指令集组合。

3 RISC-V指令格式

3.1 指令表述

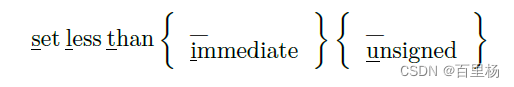

在RISC-V中,指令是通过如下图方式,表述的:

图中,从左到右连接带下划线的字母,即可描述若干条指令。

- 大括号{ } 内列举了每组指令的所有变体。

- 这些变体通过带下划线的字母,和不表示任何字母的下划线_ 区分。

例如,上图表示slt、slti、sltu、sltiu 这4 条RV32I 指令。

3.2 指令格式

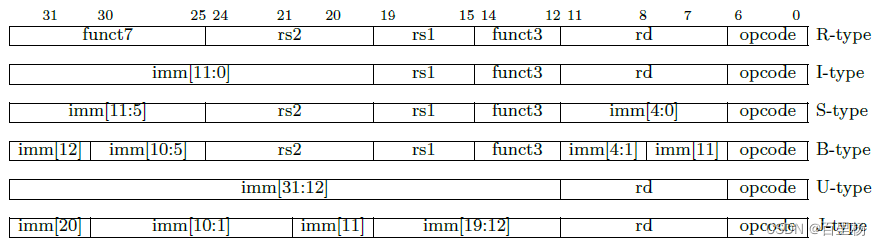

RISC-V 只有6 种指令格式,每条指令都是32 位。

- R 型指令,用于寄存器间操作

- I 型指令,用于短立即数和取数(load)操作

- S 型指令,用于存数(store)操作

- B 型指令,用于条件分支跳转

- U 型指令,用于长立即数

- J 型指令,用于无条件跳转

这6 种指令格式定义,如下图所示:

- opcode,表示操作码,固定占用[6:0]。

- rd (Destination Register),表示目的寄存器,固定占用[11:7](若存在)。

- funct3,表示操作字段,固定占用[14:12](若存在)。

- funct7,表示操作字段,固定占用[31:25](若存在)。

- rs1 (Source Register #1),表示第一个源操作数寄存器,固定占用[19:15](若存在)。

- rs2 (Source Register #2),表示第二个源操作数寄存器,固定占用[24:20](若存在)。

- imm,表示立即数,位域位置不固定,不同类型指令有不同定义。

RISC-V的所有指令,全部都是基于这6种格式来建立的。

为帮助程序员,所有位全为0 的指令,是一条非法的指令。因此,错误地易于编程/编译/链接跳转到被清零的内存区域将立即触发自陷,从而帮助调试。

类似地,所有位全为1 的指令,也是非法指令,这能在发生其他常见错误时触发自陷,如访问未编程的非易失性内存设备、断开连接的内存总线或损坏的内存芯片。

更多【risc-v-RISC-V指令格式】相关视频教程:www.yxfzedu.com

相关文章推荐

- 编程技术-docker部署Prometheus+Cadvisor+Grafana实现服务器监控 - 其他

- 编程技术-虹科示波器 | 汽车免拆检修 | 2021款广汽丰田威兰达PHEV车发动机故障灯异常点亮 - 其他

- 编程技术-Pandas教程(非常详细)(第六部分) - 其他

- 编程技术-没有设计经验的新手如何制作一本电子画册? - 其他

- 编程技术-根据关键词搜索阿里巴巴商品数据列表接口|阿里巴巴商品列表数据接口|阿里巴巴商品API接口|阿里巴巴API接口 - 其他

- 编程技术-JimuReport积木报表 v1.6.5 版本发布—免费报表工具 - 其他

- 编程技术-【Proteus仿真】【Arduino单片机】DHT11温湿度 - 其他

- 编程技术-Linux 下 JDK 安装(tar.gz版) - jdk8 - 其他

- 编程技术-前端开发好用的vscode插件 - 其他

- 编程技术-jQuery - AJAX get() 和 post() 方法 - 其他

- 编程技术-【Java 进阶篇】JQuery 案例:全选全不选,为选择添彩 - 其他

- java-java表白代码 - 其他

- 编辑器-Linux编辑器:vim的简单介绍及使用 - 其他

- 编辑器-将 ONLYOFFICE 文档编辑器与 С# 群件平台集成 - 其他

- 媒体-行业洞察:分布式云如何助力媒体与娱乐业实现创新与增长? - 其他

- 编辑器-wpf devexpress设置行和编辑器 - 其他

- 媒体-海外媒体发稿:彭博社发稿宣传中,5种精准营销方式 - 其他

- 编辑器-广州华锐互动:VR互动实训内容编辑器助力教育创新升级 - 其他

- hadoop-WPF ToggleButton 主题切换动画按钮 - 其他

- python-pytorch-gpu(Anaconda3+cuda+cudnn) - 其他

2):严禁色情、血腥、暴力

3):严禁发布任何形式的广告贴

4):严禁发表关于中国的政治类话题

5):严格遵守中国互联网法律法规

6):有侵权,疑问可发邮件至service@yxfzedu.com